## Integrated Circuit Technology Challenges

C. Michael Garner Technology & Manufacturing Group Technology Strategy April 27, 2006

# **Key Messages**

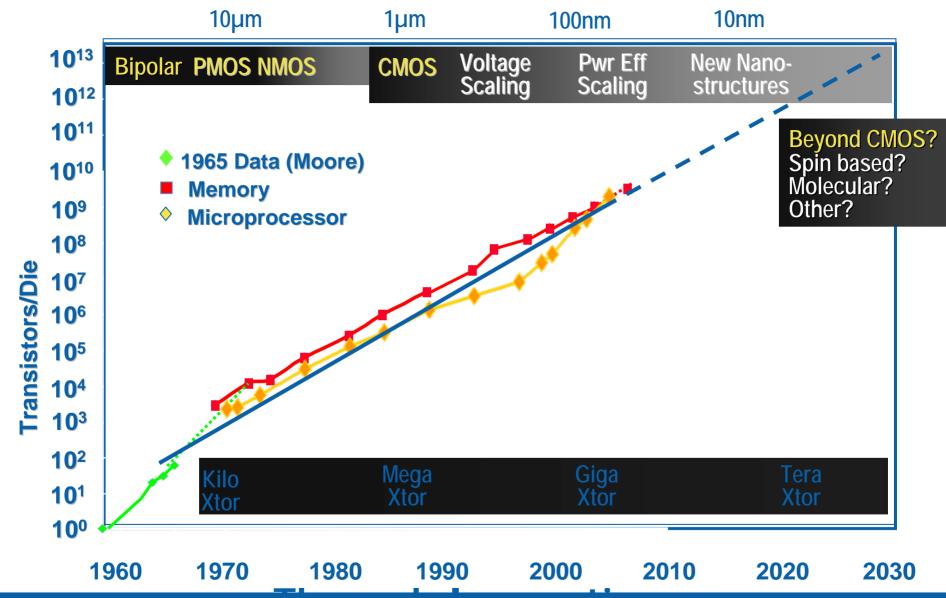

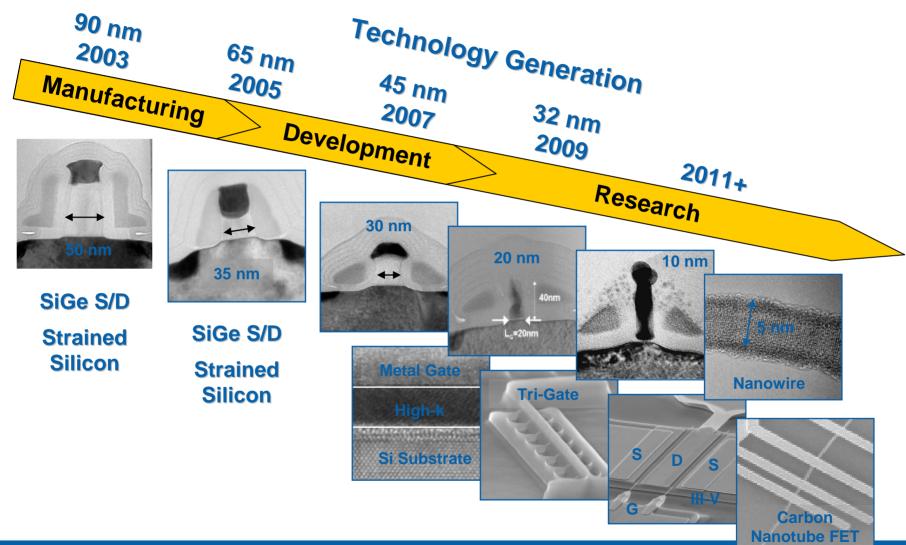

Silicon Nanoelectronics is production reality and follows Moore's law

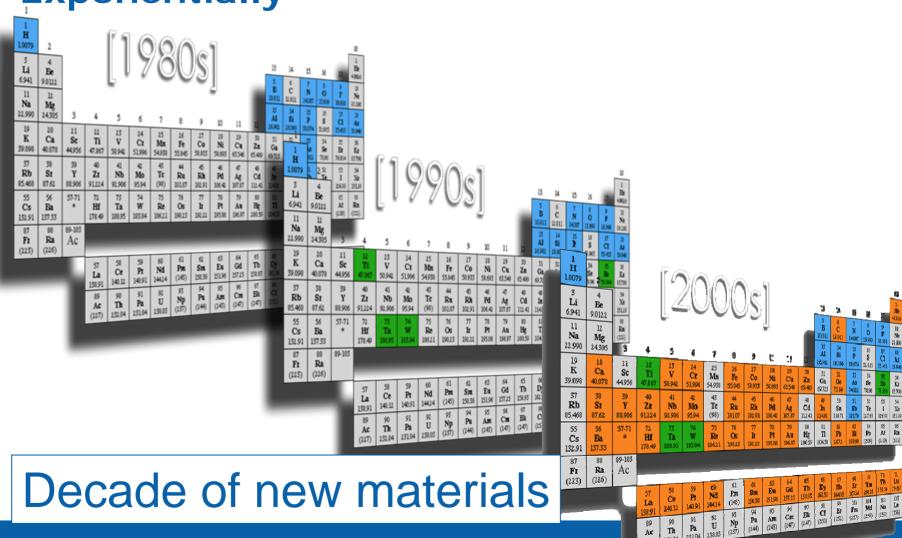

New materials are needed to extend CMOS

Long term: Novel devices will be needed to enhance CMOS

New materials, metrology, and modeling are required

Increased collaboration between Industry, Universities & Gov't is essential!!!

## **Agenda**

Moore's Law

**Extending CMOS**

**Emerging Research Memory Devices**

**Revolutionary CMOS**

**Device options to enhance CMOS (Beyond CMOS)**

**Nanomaterial Challenges**

**Summary**

#### Moore's Law Will Outlive CMOS

## Innovation-Enabled Pipeline in Place

Future options subject to change

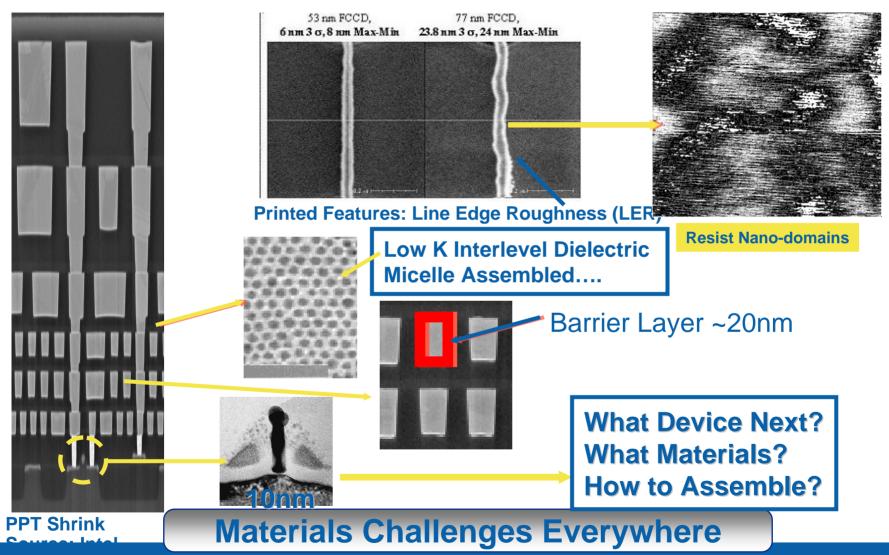

## **Material Challenges**

## Si Technology: Complexity Increasing Exponentially

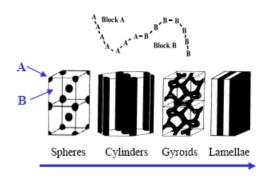

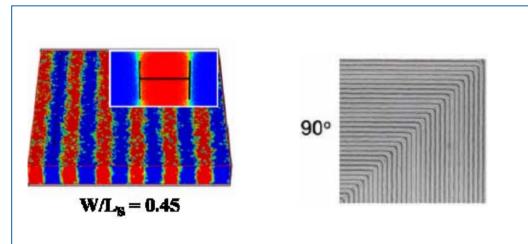

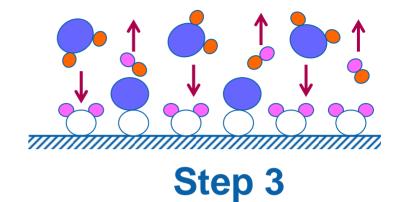

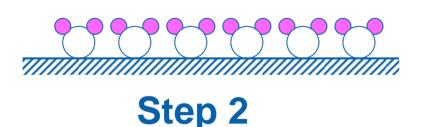

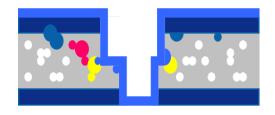

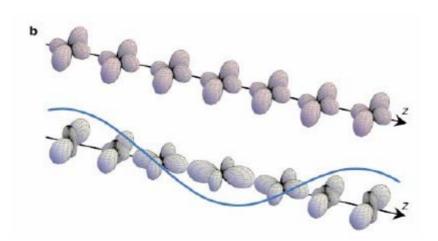

#### **Directed Self Assembly Progress**

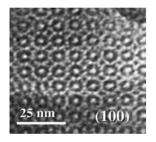

Di-block Copolymer self assembly on patterned Molecular monolayer: Goal reduce LER P. Nealey, U. Wisc.

Di-block Copolymer self assembly of magnetic materials in a confined space. C. Ross, MIT

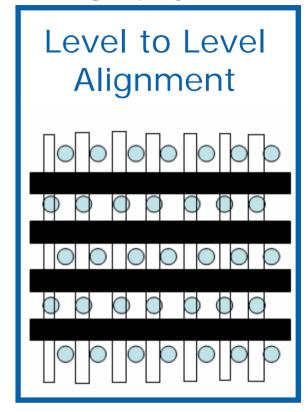

Progress in aligning self assembled structures with lithographically defined structures

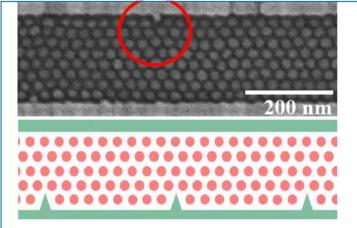

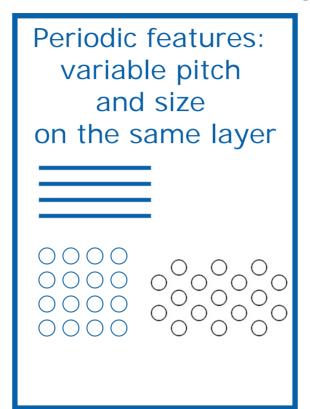

#### **Sublithographic Directed Self Assembly Lithography**

- Self Assembly may be used in nonaligned applications

- •To Extend lithography, the challenges are significant!!

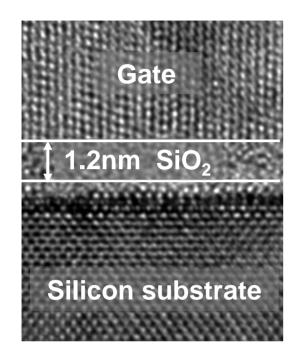

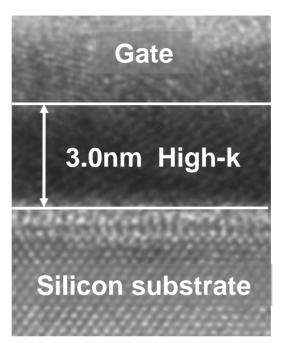

#### High-k Dielectric reduces leakage substantially

Robert Chau, Nov., 2003

#### Benefits compared to current process technologies

|                            | High-k vs. SiO <sub>2</sub> | Benefit                    |

|----------------------------|-----------------------------|----------------------------|

| Capacitance                | 60% greater                 | Much faster<br>transistors |

| Gate dielectric<br>leakage | > 100x reduction            | Far cooler                 |

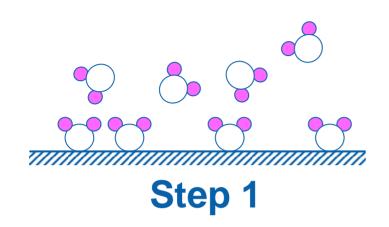

#### High-k Materials Require New Manufacturing Techniques

High-k Materials Are Deposited One Molecular Layer at a Time Precursors must be Designed for Monolayer Assembly

#### **New Interconnect Materials**

# Changes Made

**Metal lines**

AI→ Cu

**Insulating** dielectric

SiO<sub>2</sub> → SiOF

→ CDO

(low-k)

Future Options

New Thinner Barrier Layers

Ultra Low-k Dielectric

**Source: Intel**

Interconnects

**Lower K Dielectrics Needed**

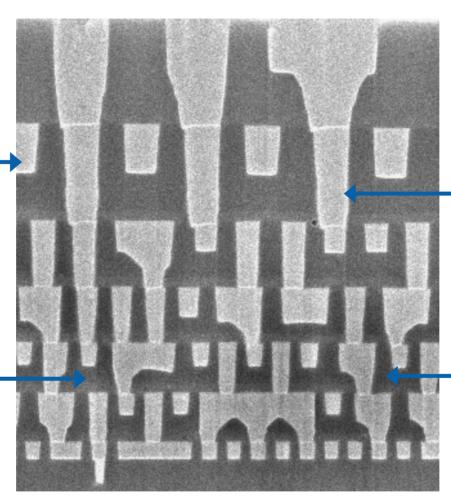

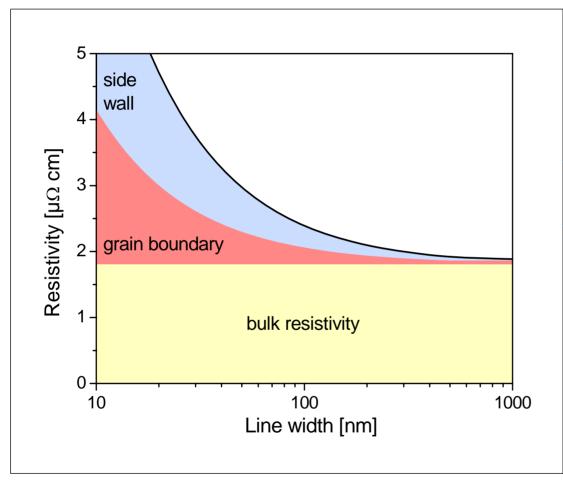

## **Small Line Conductivity**

Challenge

Reduce grain scattering

Increase grain size

Reduce sidewall scattering

Reduce line width roughness

New smoother materials??

Semiconductor Industry Association The International Technology Roadmap for Semiconductors, 2005 edition SEMATECH: Austin, TX, 2005

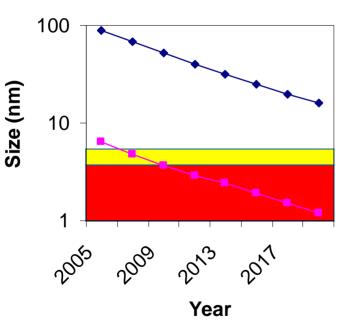

## **Cu Barrier Cladding Layer**

#### **Metal Barrier Thickness Trend**

#### **Barrier Options**

- PVD

- •CVD

- ALD Ti, Ta, W

Oxides & Nitrides

Novel Materials

Ru, etc

Semiconductor Industry Association The International Technology Roadmap for Semiconductors, 2005 edition SEMATECH: Austin, TX, 2005

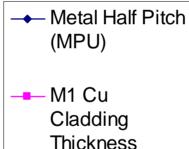

#### **Could Nanomaterials Extend Interconnect Scaling?**

Technology Research News Oct. 10, 2001

Figure 1. (a) TEM image of free-standing Au nanowires. (b) TEM image of a randomly selected Au wire showing the [111] growth direction and the electron diffraction pattern.

#### **Challenges**

- Control of location and orientation

- Control of nanostructure and properties

- Reproducibility of nanometer scale contacts

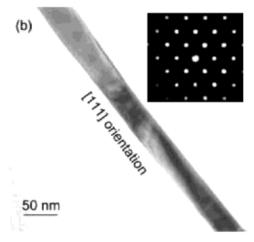

## Lower K ILD Required for Future Technologies

- Mechanical strength dropping dramatically with lower K

- Reducing K below 2.4 achieved with pores

## **Porous ILD Integration Challenge**

Pores are exposed to chemicals in Via Etch

Metal line trench etch exposes pores to even more chemicals

**Chemical Mechanical Polish & Packaging**

- Cohesive failure

- Cracking

- **Delamination**

Can novel materials protect pores from chemicals???

### **Emerging Research Memory**

Table 64 Performance Evaluation for Emerging Research Memory Device Technologies (Potential)

| Memory Device<br>Technologies<br>(Potential) | Scalability [A] | Performance [B] | Energy<br>Efficiency<br>[C] | OFF/ON<br>"1"/"0"<br>Ratio [D1] | Operational<br>Reliability<br>[E] | Operate<br>Temp<br>[F] *** | CMOS<br>Technological<br>Compatibility<br>[G]** | CMOS<br>Architectural<br>Compatibility<br>[H]* |

|----------------------------------------------|-----------------|-----------------|-----------------------------|---------------------------------|-----------------------------------|----------------------------|-------------------------------------------------|------------------------------------------------|

| Nano Floating<br>Gate Memory                 | 2.5             | 2.5             | 2.5                         | 2.5                             | 2.2                               | 2.7                        | 2.7                                             | 3.0                                            |

| Engineered<br>Tunnel Barrier<br>Memory       | 2.2             | 2.3             | 2.3                         | 2.3                             | 2.4                               | 2.8                        | 2.8                                             | 3.0                                            |

| Ferroelectric<br>FET Memory                  | 1.9             | 2.3             | 2.5                         | 2.2                             | 2.0                               | 3.0                        | 2.6                                             | 3.0                                            |

| Insulator<br>Resistance<br>Change Memory     | 2.5             | 2.5             | 2.0                         | 2.2                             | 1.9                               | 2.8                        | 2.6                                             | 2.8                                            |

| Polymar Memory                               | 2.1             | 1.5             | 2.3                         | 2.2                             | 1.6                               | 2.9                        | 2.3                                             | 2.5                                            |

| Molecular<br>Memory                          | 2.3             | 1.5             | 2.4                         | 1.6                             | 1.4                               | 2.6                        | 1.9                                             | 2.3                                            |

Semiconductor Industry Association The International Technology Roadmap for Semiconductors, 2005 edition SEMATECH: Austin, TX, 2005

#### Ferroelectric FET has many material options

Combinations of Group II, Transition & Lanthanide oxides

Insulator Resistance Change Memory has many material and mechanism options

## **Revolutionary CMOS**

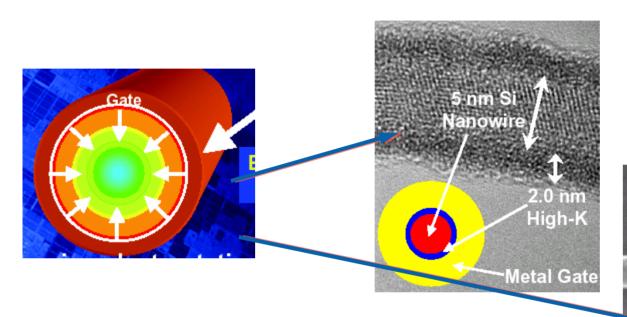

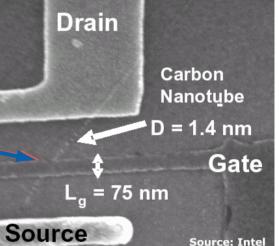

#### **Nanomaterial Transistors**

Options for sub 20nm technologies

**Challenges: Placement and property control**

**Growth Conditions & Catalysts are Critical**

#### 1D Characterization & Modeling Challenges

#### 1D Material Challenges

- Control Structure and composition (nm scale)

- Reproducible electronic properties & interactions with interface materials

- nm Scale Placement & Alignment

- Atomic Impurities & Defects

- Wafer & Device Level Property Mapping

Improved Synthesis, Models & Metrology

Needed!!!!

## **Beyond CMOS**

Vision: Devices with new functionality integrated with CMOS

#### What are we looking for?

#### Required characteristics:

- Scalability

- Performance

- Energy efficiency

- Gain

- Operational reliability

- Room temp. operation

#### Preferred approach:

- CMOS process compatibility

- CMOS architectural compatibility

#### Alternative state variables

Spin-electron, nuclear, photon

Phase

Quantum state

Magnetic flux quanta

Mechanical deformation

Dipole orientation

Molecular state

#### **New State Variables: Potential Material Needs**

- Materials that support at least 2 stable "states"

- Passivation materials to prevent undesired state changes

- Materials that enable changes of the "state"

- Materials that enable reading the "state" of a device

- Materials to transmit "state" information between "devices"

#### nm Scale Materials & Characterization

#### New materials to enable

- Room temperature operation

- State amplification (Gain) & transport

- nm Scale devices

#### New nm scale metrology needs

- State generation, lifetimes, propagation mechanisms, diffusion lengths

- State interface transport, reflection

- State coupling & interaction with intrinsic & extrinsic fields

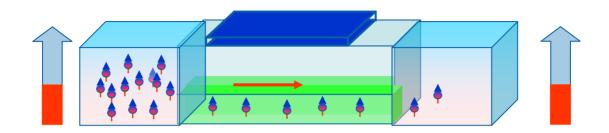

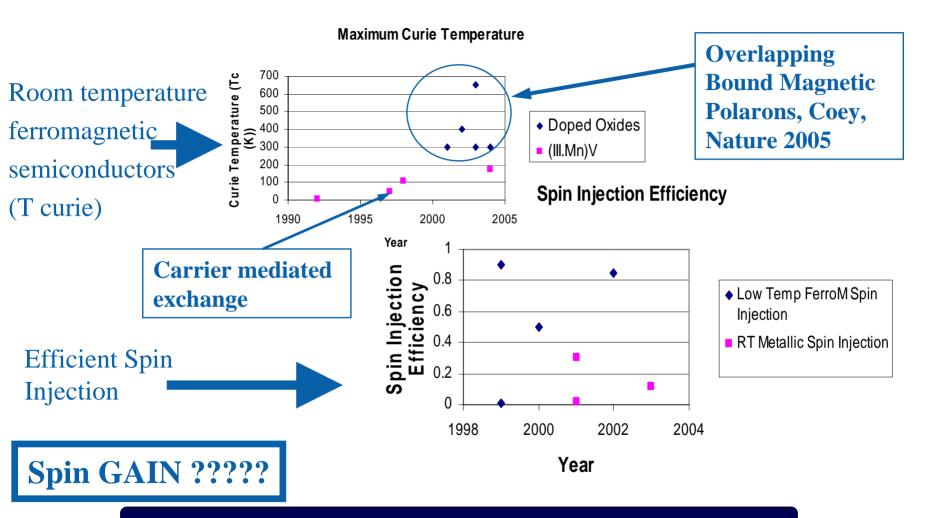

## **Spin State Material Progress**

**Need Room Temp FM Semiconductor & Spin Gain**

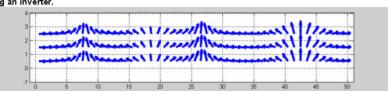

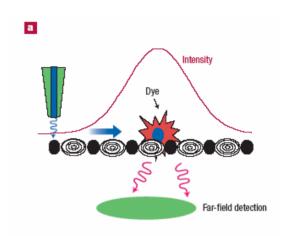

# Novel short-range energy transfer mechanisms

Figure 8. Supporting data. Plan view of the chip. Simulation demonstrating formation of ferromagnetic domains in a wire due to propagation of the spin-orbital wave. This feature provides a natural way for making an inverter.

Spin waves, Nikonov, Intel

Orbitron waves, Tokura, U of Tokyo

Plasmons – Atwater, Caltech

Coherent phonons -Stoyananov, MIT

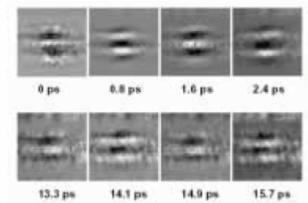

## Characterization of coupled phenomena at the nanoscale

### **Challenges:**

- \* Resolving single spin, charge and impurities

- Spin wave entanglement and propagation

- Magnetic coupling between and among nanodomains

- Nano-characterization of interface and surface effects

- Novel test structures/methods to deconvolve effects, when possible

## **Nanomaterial Challenges**

#### Nano-structured Materials

**Sub 100nm particles**

Molecular Assembly (directed & self assembly)

Source: J. Brinker, UNM/Sandia National Labs

**Macromolecules**

**Property Control, Contact Resistance and Metrology are Critical**

## Nano-material Challenges

Significantly improve material performance

Low integration complexity

Controlled assembly into useful forms

**Control & reproducibility of properties**

**Purity**

Metrology

**Environmental Health & Safety Data**

Cost

Nano-materials are often difficult to use!!!

## **Summary**

# Summary

Silicon Nanoelectronics is production reality and follows Moore's law

New materials are needed to extend CMOS

Long term: Novel devices will be needed to enhance CMOS

New materials, metrology, and modeling are required

Increased collaboration between Industry, Universities & Gov't is essential!!!